# FS7M0880

# Fairchild Power Switch(FPS)

### **Features**

- · Precise Fixed Operating Frequency

- FS7M0880(66kHz)

- Pulse By Pulse Current Limiting

- Over Current Protection

- · Over Load Protection

- Over Voltage Protection (Min. 25V)

- · Internal Thermal Shutdown Function

- Under Voltage Lockout with Hysteresis

- · Internal High Voltage Sense FET

- · Latch Up Mode

- · Soft Start

## **Description**

The Fairchild Power Switch (FPS) product family is specially designed for an off line SMPS with minimal external components. The Fairchild Power Switch (FPS) consists of high voltage power SenseFET and current mode PWM controller. The PWM controller includes integrated fixed oscillator, under voltage lock out, leading edge blanking block, optimized gate turnon/turn-off driver, thermal shut down protection, over voltage protection, temperature compensated precise current sources for loop compensation and fault protection circuit. Compared to discrete MOSFET and PWM controller or ring choke converter (RCC) solutions, the Fairchild Power Switch (FPS) can reduce total cost, component count, size and weight simultaneously increasing efficiency, productivity, and system reliability. It has simple applications well suited for cost down design for flyback converter or forward converter.

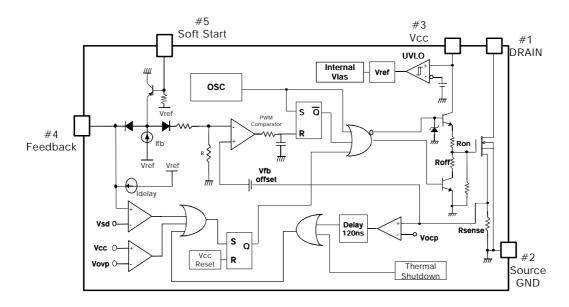

## **Internal Block Diagram**

# **Absolute Maximum Ratings**

| Parameter                                        | Symbol              | Value       | Unit |

|--------------------------------------------------|---------------------|-------------|------|

| Maximum Drain Voltage (1)                        | V <sub>D</sub> ,MAX | 800         | V    |

| Drain-Gate Voltage (RGS=1MΩ)                     | VDGR                | 800         | V    |

| Gate-Source (GND) Voltage                        | Vgs                 | ±30         | V    |

| Drain Current Pulsed (2)                         | IDM                 | 32.0        | ADC  |

| Single Pulsed Avalanche Energy (3)               | EAS                 | 810         | mJ   |

| Avalanche Current (4)                            | IAS                 | 15          | A    |

| Continuous Drain Current (Tc=25°C)               | ID                  | 8.0         | ADC  |

| Continuous Drain Current (T <sub>C</sub> =100°C) | ID                  | 5.6         | ADC  |

| Maximum Supply Voltage                           | VCC,MAX             | 30          | V    |

| Input Voltage Range                              | VFB                 | -0.3 to VSD | V    |

| Total Dawar Dissipation                          | PD                  | 190         | W    |

| Total Power Dissipation                          | Derating            | 1.54        | W/°C |

| Operating Ambient Temperature                    | TA                  | -25 to +85  | °C   |

| Storage Temperature                              | T <sub>STG</sub>    | -55 to +150 | °C   |

### Note:

- 1.  $T_j = 25^{\circ}C$  to  $150^{\circ}C$

- 2. Repetitive rating: Pulse width limited by maximum junction temperature

- 3. L = 24mH, V<sub>DD</sub> = 50V, R<sub>G</sub> = 25 $\Omega$ , starting Tj =25 $^{\circ}$ C

- 4. L = 13 $\mu H$ , starting  $T_j = 25^{\circ} C$

# **Electrical Characteristics (SFET part)**

(Ta=25°C unless otherwise specified)

| Parameter                                     | Symbol  | Condition                                                                       | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|---------|---------------------------------------------------------------------------------|------|------|------|------|

| Drain-Source Breakdown Voltage                | BVDSS   | VGS=0V, ID=50μA                                                                 | 800  | -    | -    | V    |

| Zero Gate Voltage Drain Current               | Inco    | VDS=Max., Rating,<br>VGS=0V                                                     | -    | -    | 50   | μΑ   |

| Zero Gate Voltage Drain Gurrent               | IDSS    | V <sub>DS</sub> =0.8Max., Rating,<br>V <sub>GS</sub> =0V, T <sub>C</sub> =125°C | -    | 1    | 200  | μΑ   |

| Static Drain-Source On Resistance (note1)     | RDS(ON) | VGS=10V, ID=5.0A                                                                | -    | 1.2  | 1.5  | Ω    |

| Forward Transconductance (note1)              | gfs     | V <sub>DS</sub> =15V, I <sub>D</sub> =5.0A                                      | 1.5  | 2.5  | -    | S    |

| Input Capacitance                             | Ciss    | \\ \\\\\\ \\\\\\\\\\\\\\\\\\\\\\                                                | -    | 2460 | -    | pF   |

| Output Capacitance                            | Coss    | VGS=0V, VDS=25V,<br>f=1MHz                                                      | -    | 210  | -    |      |

| Reverse Transfer Capacitance                  | Crss    | 1-111112                                                                        | -    | 64   | -    |      |

| Turn On Delay Time                            | td(on)  | V <sub>DD</sub> =0.5BV <sub>DSS</sub> , I <sub>D</sub> =8.0A                    | -    | -    | 90   |      |

| Rise Time                                     | tr      | (MOSFET switching time are essentially                                          | -    | 95   | 200  | nS   |

| Turn Off Delay Time                           | td(off) | independent of                                                                  | -    | 150  | 450  | 113  |

| Fall Time                                     | tf      | operating temperature)                                                          | -    | 60   | 150  |      |

| Total Gate Charge<br>(Gate-Source+Gate-Drain) | Qg      | VGS=10V, ID=8.0A,<br>VDS=0.5BVDSS (MOSFET                                       | -    | -    | 150  |      |

| Gate-Source Charge                            | Qgs     | switching time are                                                              | -    | 20   | -    | nC   |

| Gate-Drain (Miller) Charge                    | Qgd     | essentially independent of operating temperature)                               | -    | 70   | -    |      |

### Note:

1. Pulse test: Pulse width  $\leq 300\mu S$ , duty cycle  $\leq 2\%$ 2.  $S = \frac{1}{R}$

# Electrical Characteristics (CONTROL part) (Continued)

(Ta=25°C unless otherwise specified)

| Parameter                             | Symbol   | Condition                           | Min. | Тур. | Max. | Unit  |

|---------------------------------------|----------|-------------------------------------|------|------|------|-------|

| UVLO SECTION                          |          |                                     |      | I    | I    | 1     |

| Start Threshold Voltage               | VSTART   | -                                   | 14   | 15   | 16   | V     |

| Stop Threshold Voltage                | VSTOP    | After turn on                       | 8    | 9    | 10   | V     |

| OSCILLATOR SECTION                    |          |                                     |      |      | I    | •     |

| Initial Frequency                     | Fosc     | -                                   | 60   | 66   | 72   | kHz   |

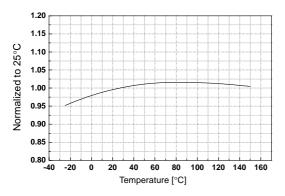

| Frequency Change With Temperature (2) | ΔF/ΔΤ    | -25°C ≤ Ta ≤ +85°C                  | -    | ±5   | ±10  | %     |

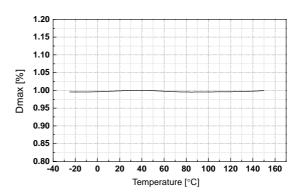

| Maximum Duty Cycle                    | Dmax     | -                                   | 45   | 50   | 55   | %     |

| Voltage Stability                     | Fstable  | 12V ≤ Vcc ≤ 23V                     | 0    | 1    | 3    | %     |

| FEEDBACK SECTION                      |          |                                     |      |      | I.   |       |

| Feedback Source Current               | IFB      | Ta=25°C, 0V ≤ Vfb ≤ 3V              | 0.7  | 0.9  | 1.1  | mA    |

| Shutdown Delay Current                | Idelay   | Ta=25°C, 5V ≤ Vfb ≤ V <sub>SD</sub> | 4.0  | 5.0  | 6.0  | μΑ    |

| Shutdown Feedback Voltage             | Vsd      |                                     | 6.9  | 7.5  | 8.1  | V     |

| SOFT START SECTION                    |          |                                     |      |      |      | •     |

| Soft Start Voltage                    | Vss      | V <sub>FB</sub> =2V                 | 4.7  | 5.0  | 5.3  | V     |

| Soft Start Resistor                   | Rsoft    | Bias=Vref, SS=0V                    | 17.0 | 18.5 | 21.0 | kΩ    |

| REFERENCE SECTION                     |          |                                     |      | •    | •    |       |

| Output Voltage (1)                    | Vref     | Ta=25°C                             | 4.80 | 5.00 | 5.20 | V     |

| Temperature Stability (1)(2)          | Vref/∆T  | -25°C ≤ Ta ≤ +85°C                  | -    | 0.3  | 0.6  | mV/°C |

| CURRENT LIMIT (SELT-PROTECTION)S      | ECTION   |                                     |      | •    | •    |       |

| Peak Current Limit                    | Iover    | Max. inductor current               | 4.40 | 5.00 | 5.60 | А     |

| PROTECTION SECTION                    |          |                                     |      |      |      | •     |

| Thermal Shutdown Temperature (Tj) (1) | TSD      | -                                   | 140  |      |      | °C    |

| Over Voltage Protection Voltage       | Vovp     | -                                   | 25   | 28   | 31   | V     |

| Over Current Protection Voltage       | VOCP     | -                                   | 1.05 | 1.10 | 1.15 | V     |

| TOTAL DEVICE SECTION                  |          |                                     |      | •    | •    |       |

| Start Up Current                      | ISTART   | VCC=14V                             | -    | 40   | 80   | uA    |

| Operating Supply Current              | lop      | Ta=25°C                             | -    | 8    | 12   | mA    |

| (Control Part Only)                   | lop(lat) | After latch,<br>Vcc=Vstop-0.1V      | 150  | 250  | 350  | uA    |

#### Note:

- 1. These parameters, although guaranteed, are not 100% tested in production

- 2. These parameters, although guaranteed, are tested in EDS (wafer test) process

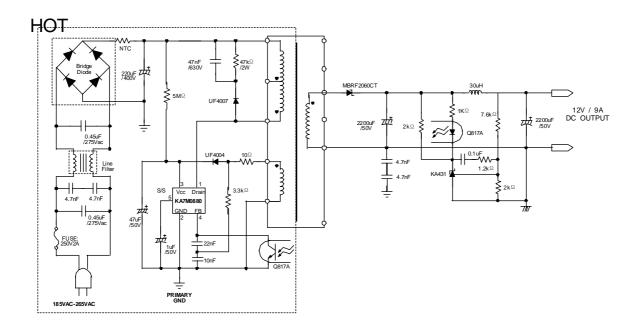

### **General Application**

In general, the FPS consists of several functional sections: under voltage lockout circuit (UVLO), reference voltage, oscillator (OSC), pulse width modulation (PWM) block, protection circuits and gate drive circuit.

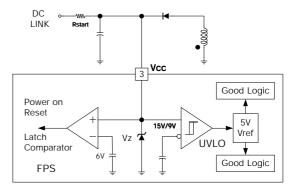

### Start-Up

The minimum current that FPS requires for the start-up is 80µA. This current can be provided by the DC link bulk capacitor (DC start-up) or directly by the AC line (AC start-up).

### DC start-up

Assuming wide range input voltage (85-265V), the maximum value of Rstart is calculated with the minimum input voltage as follows:

$$R_{start} = \frac{85\sqrt{2} - 15}{80\mu A} = 1.3M\Omega$$

The maximum power dissipation in Rstart is calculated with the maximum input voltage as follows:

Ploss =

$$\frac{(265\sqrt{2}-15)^2}{1.3M\Omega}$$

= 0.1(W)

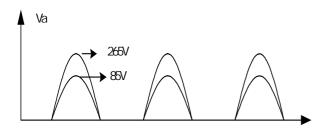

### AC start-up

When the start-up current is provided directly by the AC line through a single rectifier diode, the maximum value of Rstart is calculated with the minimum input voltage as follows:

$$R_{Start} = \frac{2 \cdot 85 \sqrt{2} - 15\pi}{2\pi} \div (80 \mu A)$$

The maximum power dissipation in Rstart is calculated with the maximum input voltage as follows:

$$Va(rms) = \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} (Vp \sin t - 15)^{2} dt$$

$$= 177V(Vp = 265\sqrt{2})$$

$$P_{loss} = \frac{Va(rms)^{2}}{Rstart} = \frac{(177)^{2}}{380k}$$

$$= 82(mW)$$

The current provided through the starting resistor charges the Vcc capacitor. When Vcc becomes higher than the threshold voltage, the FPS starts the switching operation of the built-in

power MOSFET. Then, the current required by the control IC is suddenly increased to 7mA, which makes it difficult for FPS to operate with the current provided through Rstart. Therefore, after FPS starts, the auxiliary winding of the transformer should supply most of the power required by the FPS. It is suitable to use an appropriately sized  $V_{CC}$  capacitor, generally about 33 $\mu$ F, because the starting time can be delayed if it is too large. This operation is described in figure 2. Although  $V_{CC}$  needs to be set only above 9V during the normal operation, it should be set to such an extent that over voltage protection (OVP) is not activated during an overload condition. For full load, about 18~20V is appropriate for  $V_{CC}$  and for no load, about 13~14V is suitable.

#### **Protection**

The FPS has not only pulse by pulse current limit circuit, but also several self-protection circuits. These protection circuits are fully integrated and do not require external components. After the protection circuits are activated, the FPS completely stops the SMPS (Latch Mode Protection) until the power on reset circuit is activated by removing and restoring input power, or restarts the SMPS automatically (Auto Restart Mode Protection).

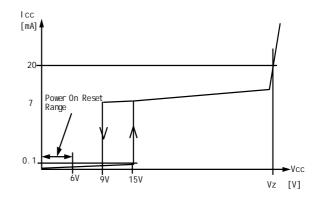

Figure 1. Undervoltage lockout (UVLO) circuit

These two operations are user-selected operations, so the user can select proper device according to the shutdown mode. The operations principle and applications for each protection are described as follows.

Figure 2. Variation of Icc according to Vcc

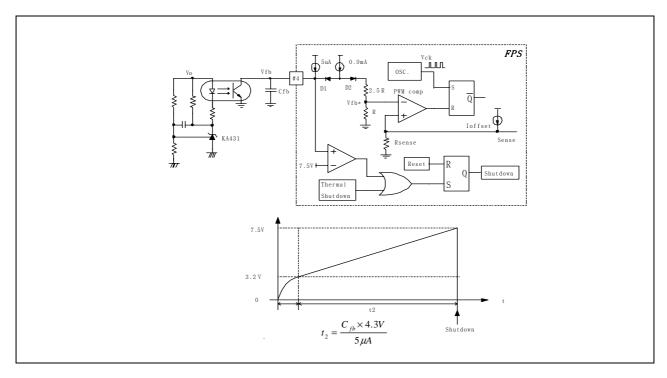

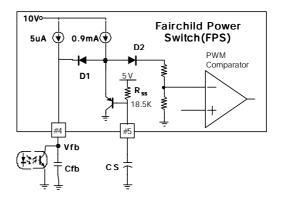

Figure 3. Pulse-width-modulation (PWM) block

#### Pulse by pulse current limit

Figure 3 shows the pulse-width-modulation (PWM) block of the FPS. Since the FPS employs the peak current mode control, the current through the power MOSFET is limited by the inverting input voltage of PWM comparator (Vfb\*). Assuming that the 0.9mA current source flows only through the internal resistor (2.5R + R = 2.8k) and the diode forward voltage drop is 0.7V, the anode voltage of diode D2 is about 3.2V. Since D1 is blocked when the feedback voltage (Vfb) exceeds 3.2V, the maximum voltage of the anode of D2 is 3.2V. Therefore, the maximum value of Vfb\* is about 0.7V, which determines the maximum current through the power MOSFET.

#### **Over Load Protection**

Overload means that the load current exceeds a pre-set level due to the abnormal situation. In this situation, protection circuit should be activated in order to protect the SMPS. However, even when the SMPS is in the normal operation, the over load protection circuit can be activated during the load transition. In order to avoid this undesired operation, the over load situation should be distinguished from the normal load transition situation. As a measure against this problem, over load protection circuit in the FPS is designed to be activated after a specified period to determine whether it is a transient situation or an overload situation. The protection circuit is allowed to shut down the SMPS only when the over load condition continues longer than preset period. The detailed operation principle is explained in figure 3. Because of the pulse by pulse current limit circuit, the maximum current through the FPS is limited, and therefore the maximum

input power is restricted with a given input voltage. If the output consumes beyond this maximum power, the output voltage (Vo) decreases below the set voltage. This reduces the current through the opto-coupler diode, which also reduces opto-coupler transistor current increasing Vfb. If Vfb exceeds 3.2V, D1 is blocked and the 5µA current source starts to charge Cfb slowly compared to when the 0.9mA current source charges Cfb. Vfb continues increasing until it reaches 7.5V, and the FPS shuts down at that time. The delay time for shutdown is the time required to charge Cfb from 3.2V to 7.5V with  $5\mu A$ . When Cfb is 10nF (103), t2 is approximately 8.6mS and when Cfb is 0.1µF (104), t2 is approximately 86ms. These values are enough to prevent SMPS from being shut down for most transient situations. Just increasing Cfb to obtain a longer delay time may cause problems, because Cfb is an important parameter for determining the response speed of the SMPS. To solve this problem, auxiliary capacitor in series with zener diode can be used in parallel with Cfb. The breakdown voltage of the zener diode should be about 3.9 ~ 4.7V. When Vfb is below the zener voltage, the system dynamics is determined by Cfb. When Vfb exceeds the zener voltage, the delay time is determined by the auxiliary capacitor. By using large auxiliary capacitor, the delay time can be extended without sacrifice of the dynamic response.

#### Over voltage Protection (OVP) Circuit

The FPS has a self-protection feature against malfunctions, such as feedback circuit open or short-circuit. When the feedback terminal is open due to a malfunction in the secondary side feedback circuit or a defect of solder, the current through the opto-coupler transistor becomes almost zero.

Then, Vfb continues increasing and the preset maximum current flows through the primary side until the over load protection circuit is activated. Since maximum current is transferred to the secondary side, the secondary side voltage becomes much higher than the rated voltage. If there is no protection circuit against over voltage, the devices in the secondary side will be damaged. In order to prevent this situation, the FPS has an over voltage protection circuit (protection against feedback circuit abnormalities). In general, Vcc is proportional to the output voltage and FPS uses Vcc instead of directly monitoring the output voltage to detect over voltage situation. If VCC exceeds 24 V, the FPS activates the OVP circuit. Therefore, VCC should be properly designed to be below 24V during normal operation to avoid the undesired activation of OVP.

#### **OCP (Over Current Protection)**

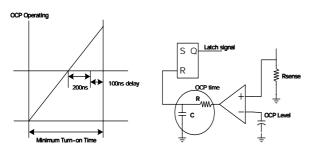

Figure 4. OCP Function & Block

Even though the FPS has OLP (Over Load Protection) and pulse by pulse current limiting feature, these are not enough to protect FPS when a secondary side diode short or load short occurs. Therefore, FPS has internal OCP (Over Current Protection) circuit as shown in figure 4. When the gate turn-on signal is applied to the power MOSFET, the OCP block is enabled and monitors the current through the sensing resistor for lus. The voltage across the resistor is compared with the preset OCP level. If the sensing resistor voltage is greater than the OCP level for longer than 200ns within the allowed comparison time of 1us, the reset signal is applied to the latch, resulting in the shutdown of SMPS. Here, the additional delay of 100ns after the 200ns delay is the time required for the operation of the protection circuit.

### Soft start operation

At startup, the voltage of the PWM comparator inverting input is saturated to its maximum value. In that case, the power MOSFET current is at its maximum value and maximum allowable power is delivered to the secondary side until the output voltage is established. It should be noted that when the SMPS delivers maximum power to the secondary side during the startup, the entire circuit is seriously stressed. By using a soft start function, such stresses can be alleviated. Figure 5 shows how the soft-start circuit is implemented. When it starts up, the soft start capacitor Cs on pin 5 begins to be charged through the internal resistor (Rss), which forces the comparator inverting input voltage

to increase slowly, also increasing the duty ratio slowly. When the voltage of CS reaches about 3.2V, PNP transistor is turned off and Cs continues being charged up to 5V through Rss. Then, the voltage of the comparator inverting input follows the feedback voltage of pin 4 instead of following the voltage of Cs. When the SMPS is shut down by the protection circuits, Cs is discharged through the internal resistor allowing Cs to be charged from 0V when the SMPS starts up again.

Figure 5. Soft Start Circuit

# 3. Application Note using the FPS

## -Flyback Application (100W)

# **Transformer Specification**

### 2. Winding Specification

| No.                                                   | $PIN(S\toF)$                                    | WIRE                | TURNS | WINDING METHOD   |  |  |

|-------------------------------------------------------|-------------------------------------------------|---------------------|-------|------------------|--|--|

| NP/2                                                  | 1 → 3                                           | 0.4 $\phi \times 1$ | 42    | SOLENOID WINDING |  |  |

|                                                       | INSULATION : POLYESTER TAPE t = 0.050mm, 1Layer |                     |       |                  |  |  |

| N+12V                                                 | 12 → 13                                         | 14mm × 1            | 8     | COPPER WINDING   |  |  |

|                                                       | INSULATION : POLYESTER TAPE t = 0.050mm, 3Layer |                     |       |                  |  |  |

| NB                                                    | 8 → 7                                           | 0.3 $\phi \times 1$ | 9     | SOLENOID WINDING |  |  |

|                                                       | INSULATION : POLYESTER TAPE t = 0.050mm, 1Layer |                     |       |                  |  |  |

| NP/2                                                  | 3 → 4                                           | 0.4 $\phi \times 1$ | 42    | SOLENOID WINDING |  |  |

| OUTER INSULATION : POLYESTER TAPE t = 0.050mm, 3Layer |                                                 |                     |       |                  |  |  |

### 3. Electical Characteristic

| CLOSURE    | PIN   | SPEC.      | REMARKS       |

|------------|-------|------------|---------------|

| INDUCTANCE | 1 - 4 | 700uH ±10% | 1kHz, 1V      |

| LEAKAGE L  | 1 - 4 | 10uH MAX.  | 2nd ALL SHORT |

### 4. Core & Bobbin

CORE: EER 4042 BOBBIN: EER4042

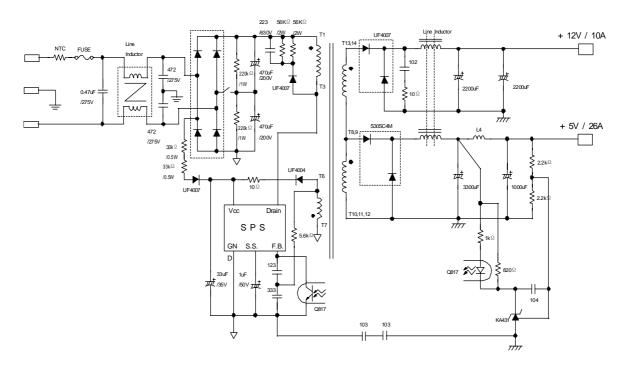

### -Forward Application (250W)

# **Transformer Specification**

## 2. Winding Specification

|       | T                 |          | I     | I .              |

|-------|-------------------|----------|-------|------------------|

| No.   | PIN(S → F)        | WIRE     | TURNS | WINDING METHOD   |

| NP/2  | 1 → 3             | 0.65 φ×1 | 50T   | SOLENOID WINDING |

| N+5V  | 8, 9 → 10, 11, 12 | 14mm × 1 | 4T    | COPPER WINDING   |

| N+12V | 13, 14 → 9        | 0.65 φ×4 | 5T    | SOLENOID WINDING |

| NP/2  | 1 → 3             | 0.65 φ×1 | 50T   | SOLENOID WINDING |

| Nvcc  | 7 → 6             | 0.65 φ×1 | 6T    | SOLENOID WINDING |

### 3. Electical Characteristic

| CLOSURE    | PIN   |

|------------|-------|

| INDUCTANCE | 1 - 3 |

| LEAKAGE L  | 1 - 3 |

### 4. Secondary Inductor(L2) Specipication

Core : Power Core 27 \phi 16 Grade

5V : 12T (1  $\phi \times 2$ ) 10V : 27T (1.2  $\phi \times 1$ )

# **Typical Performance Characteristics**

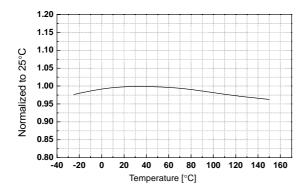

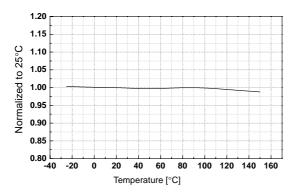

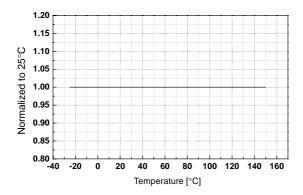

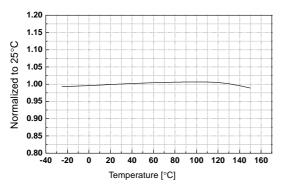

Figure 1. Operating Supply Current vs. Temp.

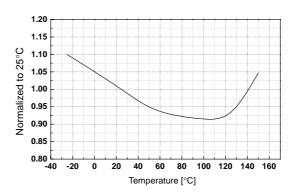

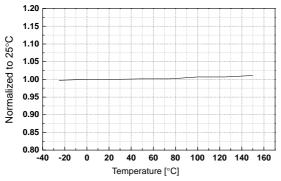

Figure 3. Start Threshold Voltage vs. Temp.

Figure 5. Operating Frequency vs. Temp.

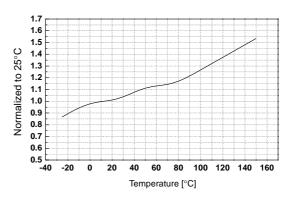

Figure 2. Start up Current vs. Temp.

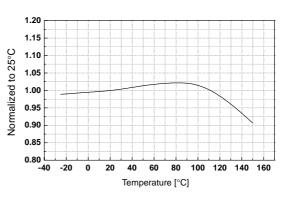

Figure 4. Stop Threshold Voltage vs. Temp.

Figure 6. Maximum Duty Cycle vs. Temp.

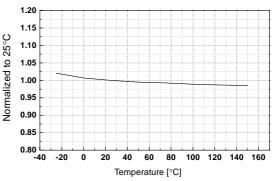

## **Typical Performance Characteristics** (Continued)

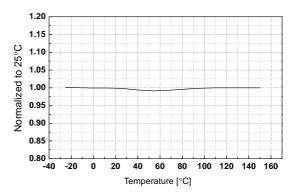

Figure 7. Minimum Duty Cycle vs. Temp.

Figure 8. Feedback Offset Voltage vs. Temp.

Figure 9. Shutdown Feedback Voltage vs. Temp.

Figure 10. Shutdown Delay Current vs. Temp.

Figure 11. SoftStart Voltage vs. Temp.

Figure 12. Over Voltage Protection vs. Temp.

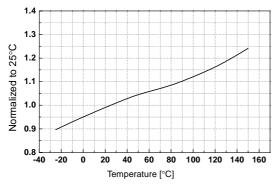

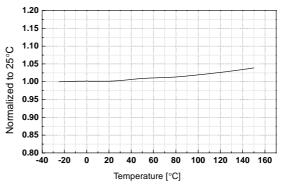

# **Typical Performance Characteristics** (Continued)

Figure 13. Feedback Sink Current vs. Temp.

Figure 14. Peak Current vs. Temp.

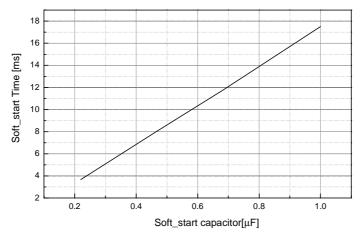

Figure 15. Soft\_start Capacitor vs. Soft\_start Temp.

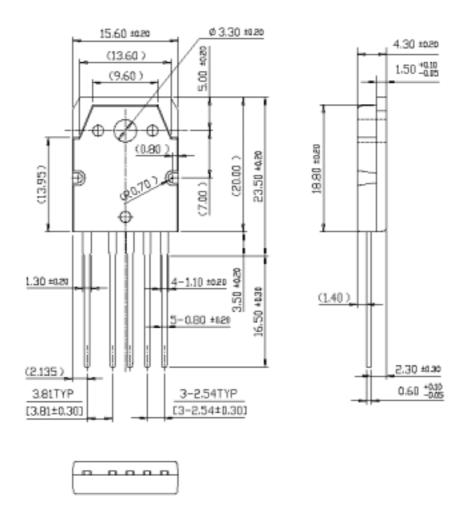

# **Package Dimensions**

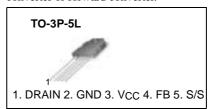

**TO-3P-5L**

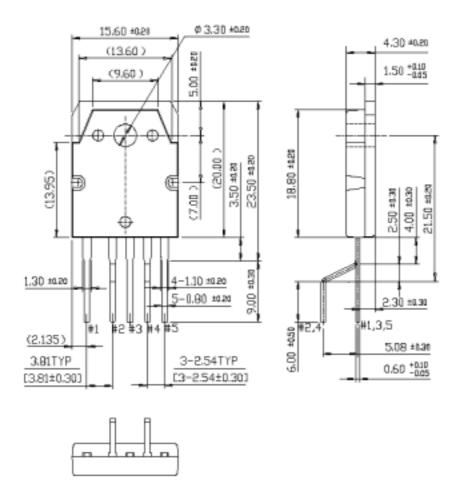

# Package Dimensions (Continued)

# TO-3P-5L (Forming)

# **Ordering Information**

| Product Number | Package           | Rating    | Fosc  |

|----------------|-------------------|-----------|-------|

| KA7M0880-TU    | TO-3P-5L          | 800V. 8A  | 67kHz |

| KA7M0880-YDTU  | TO-3P-5L(Forming) | 000 V, 0A | UINTZ |

TU : Non Forming Type YDTU : Forming type

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com